Embarking on the intricate journey of System-on-Chip (SoC) verification, I find myself navigating through a sea of tools and methodologies. In this personal exploration, the spotlight falls on two indispensable elements shaping the landscape of my verification endeavors: UVM Register and its counterpart, the UVM Register Model.

UVM Register: A Cornerstone in Verification

As a verification engineer, UVM (Universal Verification Methodology) has been my trusted companion, providing a standardized framework for crafting robust testbenches. However, delving into the intricacies of UVM Register unveiled a layer of specificity that proved to be a game-changer in the verification process.

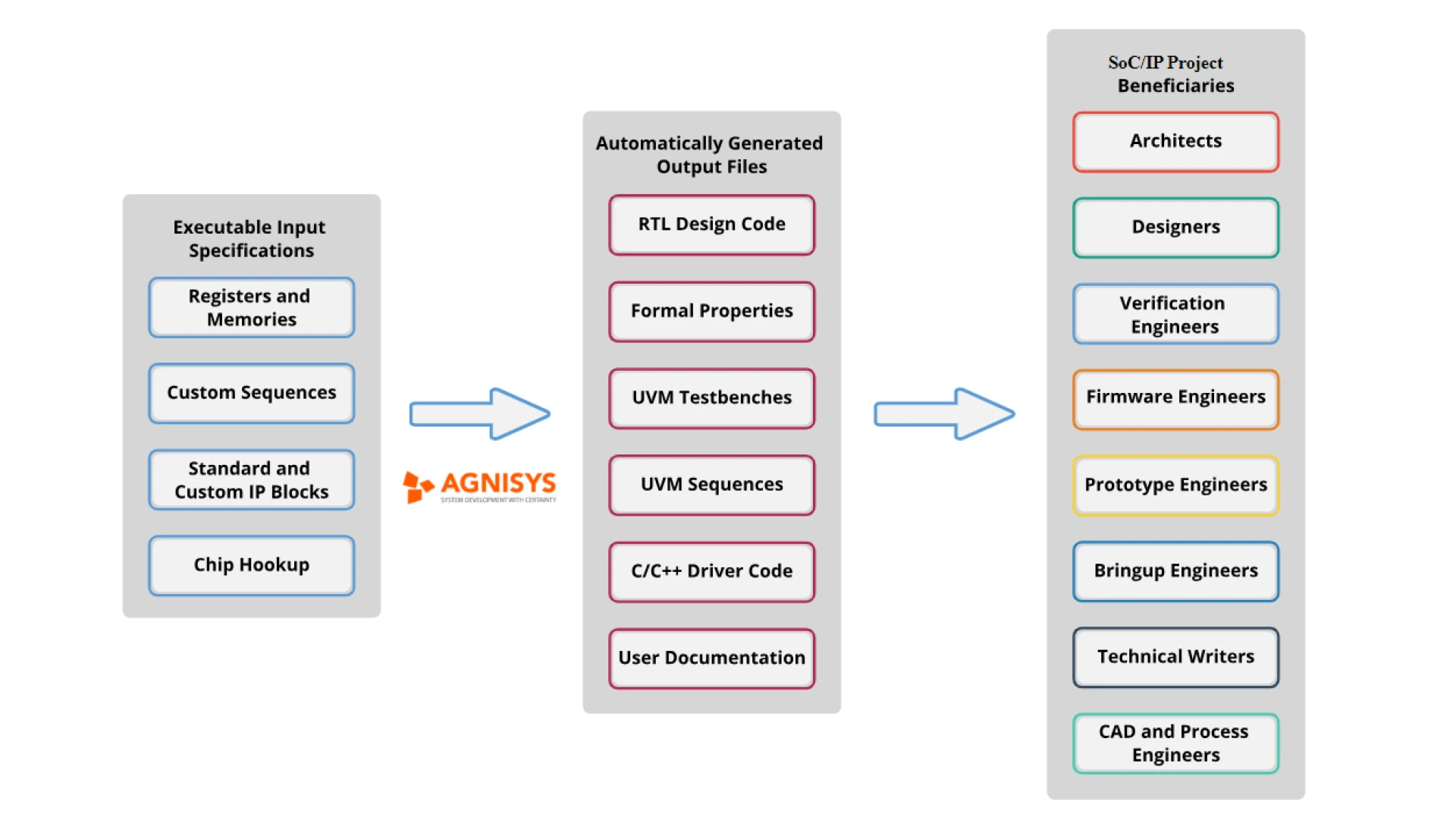

Precision in Register Modeling: UVM Register, within the UVM methodology, offers a specialized framework for modeling and verifying registers in a System-on-Chip design. It goes beyond the broader strokes of UVM, allowing me to hone in on the intricacies of registers that are fundamental to the functionality of the design.

Abstraction that Resonates: What struck me initially was the level of abstraction UVM Register brings to register modeling. It empowers me to describe registers concisely, capturing their essence without drowning in unnecessary details. This abstraction not only streamlines the modeling process but also fosters clarity in expressing the intricacies of register behavior.

Seamless Integration with UVM: The beauty of UVM Register lies in its seamless integration with the broader UVM methodology. Leveraging UVM's object-oriented architecture, UVM Register becomes a natural extension, aligning effortlessly with the overall testbench structure. This cohesion facilitates the creation of organized and scalable verification environments.

UVM Register Model: Bridging the Conceptual and Practical

As I delved deeper into the world of register verification, the UVM Register Model emerged as a guiding light, bridging the conceptual and practical aspects of my work.

A Blueprint for Register Verification: The UVM Register Model serves as a blueprint, outlining the structure and behavior of registers within the SoC. It transforms abstract register specifications into tangible components, laying the groundwork for comprehensive verification. This model becomes the reference point, ensuring that the actual implementation aligns seamlessly with the intended design.

Navigating Register Interaction with UVM Sequences: One aspect that significantly enhanced my verification capabilities was the integration of UVM Register Sequences within the UVM Register Model. These sequences provide a methodical way to navigate and verify complex register interactions. They become the building blocks for constructing test scenarios that mirror real-world usage, ensuring the robustness of the design.

The Practical Impact: A Real-world Example: What truly brought the power of UVM Register and UVM Register Model home for me was working through a real-world example. Taking a hypothetical scenario where intricate register interactions were critical, I witnessed how the UVM Register Model streamlined the verification process. The UVM Sequences, orchestrated within the model, allowed me to construct test scenarios that covered a spectrum of register behaviors, ensuring the design's resilience under diverse conditions.

The Personal Impact: A Journey of Mastery

My journey with UVM Register and UVM Register Model has been transformative. It's not just about mastering tools; it's about mastering the art of verification, about wielding these tools with precision to ensure the integrity and functionality of the designs I work on.

Efficiency in Verification: The precision in register modeling with UVM Register translates directly into efficiency in verification. With a clear and concise representation of registers, I can focus my efforts on crafting comprehensive test scenarios rather than grappling with overly detailed specifications.

Confidence in Design Integrity: The UVM Register Model serves as a compass, guiding me through the intricacies of register verification. Knowing that the abstract representation aligns with the actual design instills confidence. It transforms the verification process from a series of tests into a strategic validation of the design's integrity.

A Foundation for Continuous Learning: This personal odyssey with UVM Register and UVM Register Model is not a culmination but a foundation. As SoC designs evolve, so does my journey with these tools. The flexibility and scalability they offer ensure that I am equipped not just for today's challenges but for the ever-changing landscape of tomorrow.

In Conclusion: A Personal Evolution in Verification

In conclusion, UVM Register and its companion, the UVM Register Model, have become integral to my identity as a verification engineer. They are not just tools in my arsenal; they are the brush and palette with which I paint the landscape of verification. As I navigate the complexities of SoC design, UVM Register and its model stand as beacons, guiding me towards a future where precision, efficiency, and confidence converge in the art of verification.

Sign in to leave a comment.