Introduction: In the intricate landscape of ASIC design, precision is not just a goal—it's the very foundation of engineering excellence. This comprehensive exploration navigates the intricate paths of achieving unparalleled precision by synergizing the Universal Verification Methodology (UVM), the Register Abstraction Layer (RAL), and the strategic integration of an automated SystemRDL parser. The orchestration of these elements, coupled with UVM testbench methodologies and the UVM register model, emerges as a game-changer. Real-world UVM case studies provide concrete evidence of the transformative synergy these components bring to ASIC design.

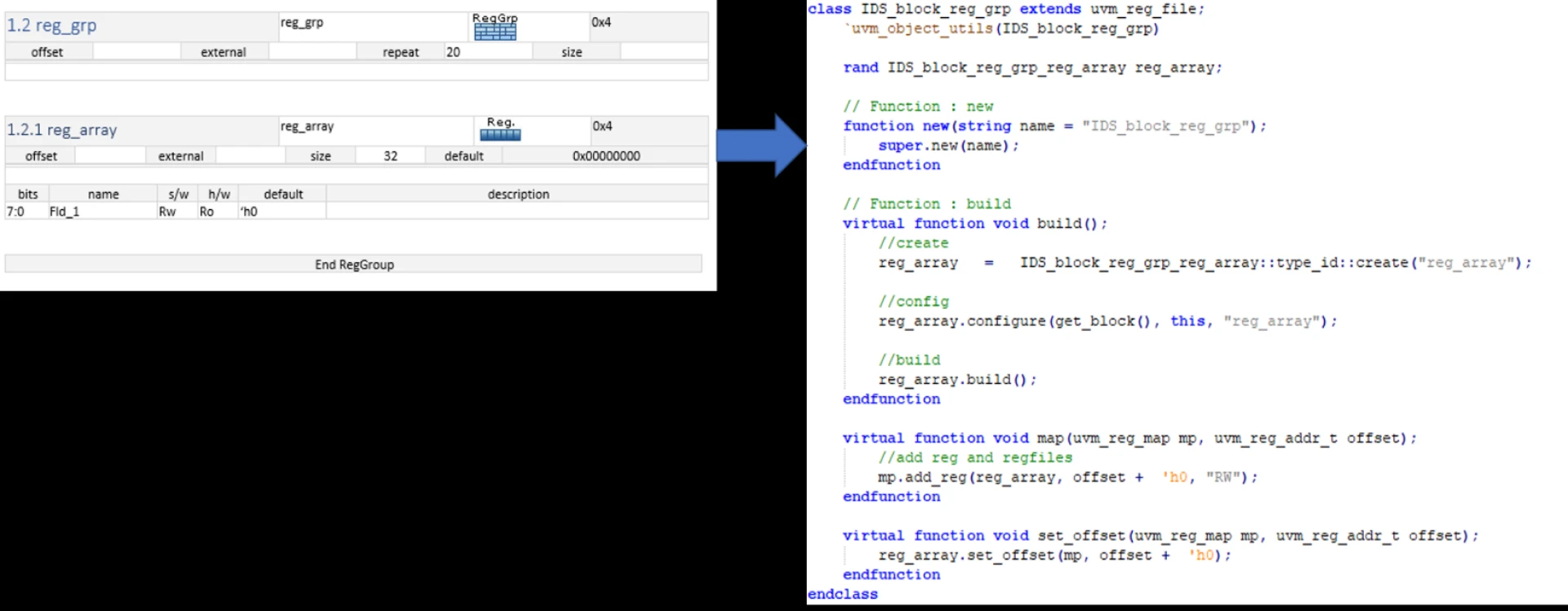

SystemRDL Parser: A Strategic Navigator: At the core of precision engineering lies the SystemRDL parser—a strategic navigator that transcends the boundaries of traditional ASIC design. This sophisticated parsing tool takes center stage, interpreting and seamlessly integrating complex register descriptions. Its role extends beyond simplifying the verification process; it introduces a layer of consistency that is instrumental for the success of ASIC designs in a rapidly evolving industry.

Automation Catalyst in UVM Testbench: Automation within the SystemRDL-driven RAL framework acts as a potent catalyst within the UVM testbench. By liberating designers from the burdens of manual efforts, it not only mitigates the risk of errors but also fosters a seamless alignment of the verification environment with the intricate register specifications. This strategic automation, intricately woven with UVM testbench methodologies, forms the backbone of precision in ASIC design.

Elegance of UVM Register Model Integration: The UVM Register model, revered as a sophisticated representation of register behavior and properties, elegantly integrates into the fabric of SystemRDL parsing. This integration process involves a meticulous translation, ensuring that any modifications in register specifications dynamically propagate to the UVM testbench. This harmonious integration enhances the overall coherence of the project, ensuring a resilient foundation for ASIC designs.

Harmony in Precision Illustrated by UVM Case Studies: The true test of precision lies in real-world scenarios. UVM case studies provide a vivid illustration of how the SystemRDL parser, UVM testbench, and UVM register model synergize to adapt to diverse scenarios. Picture an ASIC design landscape with diverse IP blocks, each presenting distinct register specifications. These case studies showcase precision, flexibility, and customization in action, providing tangible proof of the dynamic nature of this holistic approach in addressing real-world design complexities.

Strategic Solutions for Challenges: Precision engineering is not without its challenges. While automation serves as a potent tool, addressing challenges strategically becomes imperative. The diversity in register specifications across different IP blocks demands customization and flexibility in SystemRDL parsing tools. Robust error-handling mechanisms become vital to detect and rectify discrepancies, ensuring a seamless flow of precision from design to verification.

Conclusion: In conclusion, achieving unparalleled precision in ASIC design is an orchestrated symphony of tools and methodologies. The integration of an automated SystemRDL parser, seamlessly interwoven with the UVM testbench and UVM register model, represents a quantum leap forward. Real-world UVM case studies not only validate the efficacy of this precision-driven approach in expediting the verification process but also underscore its pivotal role in elevating the overall quality of ASIC designs. As the semiconductor industry propels forward, embracing this strategically orchestrated automation becomes not just advantageous but indispensable for staying at the forefront of innovation and ensuring the resilience of ASIC products in an ever-evolving market.

Sign in to leave a comment.