When you hear about FPGA Design & Development, what usually comes to mind? For many, it’s the intricate world of hardware description languages like VHDL or Verilog, long lines of code that resemble ancient scripts. But what if you could skip all that complexity and start with something closer to the software you already know?

That’s where High-Level Synthesis (HLS) steps in — transforming software-like code into custom silicon designs. It’s a game changer for engineers and developers venturing into FPGA Design & Development.

What is High-Level Synthesis (HLS)?

HLS is a design process that takes high-level programming languages — like C, C++, or SystemC — and converts them into low-level hardware descriptions. Instead of writing detailed hardware instructions by hand, you write algorithms and logic in a familiar language. The HLS tools then automatically generate the hardware logic needed to implement those algorithms on an FPGA.

This process lets engineers bridge the gap between software programming and hardware design — accelerating development cycles while maintaining the custom performance benefits of FPGAs.

Why Does HLS Matter for FPGA Design & Development?

1. Faster Development Cycles

Traditionally, FPGA Design & Development requires writing detailed RTL code, which can be time-consuming and error-prone. HLS allows developers to start at a higher level of abstraction. This means quicker iterations, easier debugging, and faster prototyping.

2. Accessibility for Software Engineers

Many developers are more comfortable with software languages than hardware description languages. HLS opens the door for software engineers to contribute directly to FPGA Design & Development without needing deep hardware design expertise.

3. Flexibility in Design

HLS offers a flexible approach to hardware design. Developers can explore multiple design options quickly by changing the high-level code and seeing the hardware impact — all without rewriting complex RTL code.

How Does the HLS Process Work?

Here’s a simplified view of the typical HLS workflow in FPGA Design & Development:

- Write High-Level Code: The process starts with writing algorithms in C/C++ or SystemC.

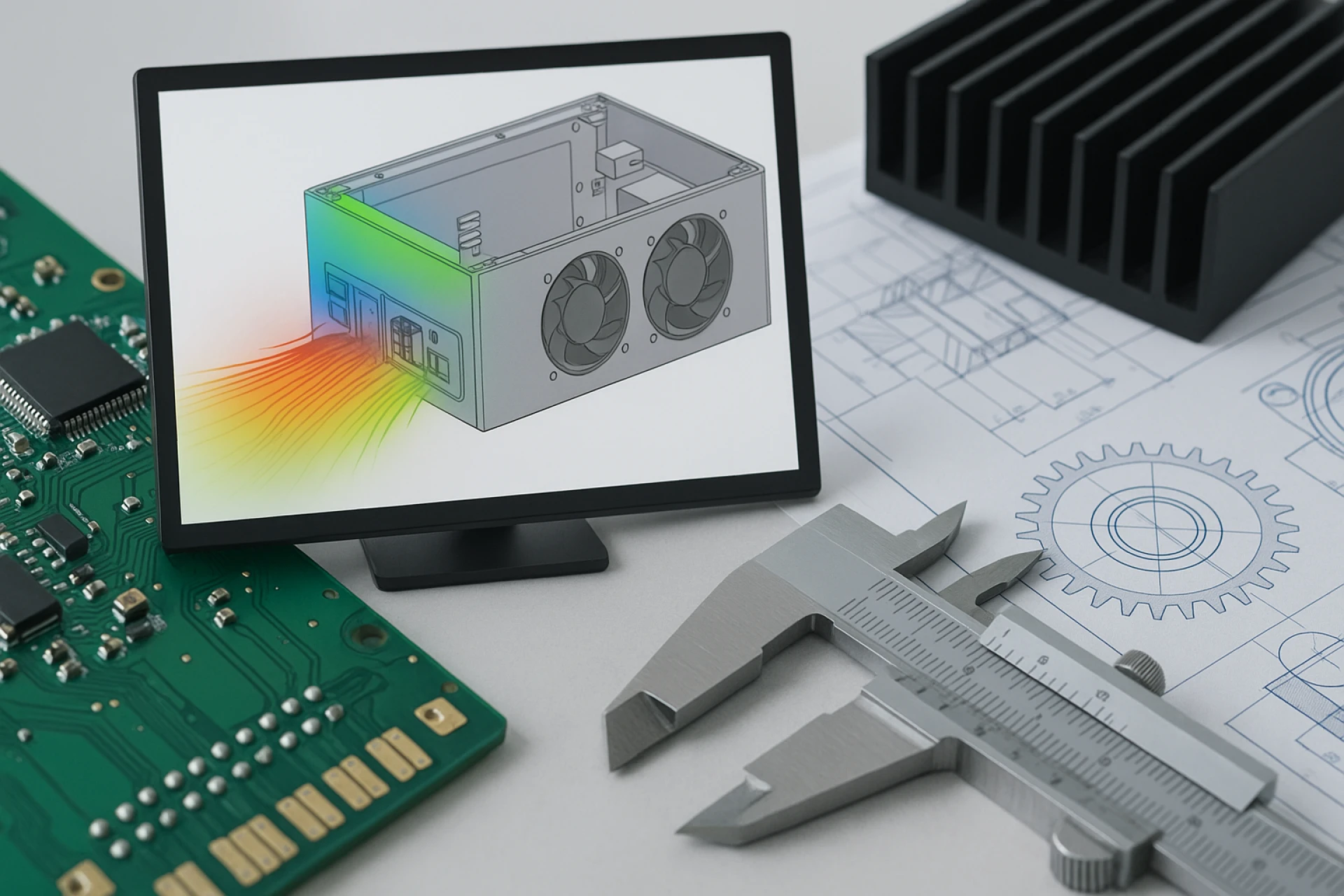

- Synthesize to RTL: HLS tools translate the high-level code into Register Transfer Level (RTL) code, typically Verilog or VHDL.

- Simulate & Optimize: The RTL is simulated to verify functionality. Developers can tweak the high-level code or synthesis directives to optimize for speed, area, or power.

- Integrate & Deploy: The RTL output integrates with the rest of the FPGA design and is deployed to the target hardware.

This process significantly streamlines FPGA Design & Development, reducing the gap between software design and hardware implementation.

Key Benefits of Using HLS in FPGA Design & Development

Improved Productivity

Writing and verifying hardware in a high-level language is faster than traditional RTL coding. This leads to shorter design cycles and faster time-to-market.

Design Reuse

High-level algorithms are often more reusable than hardware-specific code. You can reuse and adapt your C/C++ code across different projects or FPGA platforms.

Easier Debugging

High-level languages come with mature debugging tools, making it easier to find and fix issues before synthesis, compared to debugging RTL code.

When Should You Consider HLS?

HLS isn’t a silver bullet for every FPGA Design & Development project. It’s particularly helpful when:

- The design involves complex algorithms that are easier to express in software languages.

- Rapid prototyping and iteration speed matter.

- You want to leverage software engineers on your FPGA development team.

- Design flexibility and future-proofing are priorities.

Potential Challenges with HLS

While HLS simplifies many aspects, it does come with considerations:

- Learning Curve: Although easier than RTL, mastering HLS tools and optimization directives takes time.

- Performance Tuning: Achieving the same level of optimization as hand-coded RTL may require detailed understanding of synthesis pragmas and hardware architecture.

- Tool Limitations: Not all hardware constructs or optimizations are fully supported by HLS tools, which may limit some design choices.

Wrapping It Up

High-Level Synthesis is reshaping how FPGA Design & Development happens by making hardware design more accessible and faster to iterate. Whether you’re a software developer stepping into hardware or a hardware engineer looking to speed up your workflow, HLS offers a compelling way to turn your code into custom silicon.

It’s a powerful step toward democratizing FPGA Design & Development and enabling innovation without the typical steep hardware learning curve.

If you’re diving into FPGA Design & Development, understanding High-Level Synthesis is a great way to unlock new efficiencies and bring software and hardware worlds closer together.

Frequently Asked Questions (FAQs)

Q1: Does HLS replace traditional hardware design languages like Verilog or VHDL?

Not entirely. HLS generates RTL code, but developers often still need to work with RTL for integration, fine-tuning, or specific hardware control.

Q2: Can HLS-generated hardware match the performance of hand-coded RTL?

Performance can be very close, especially with good HLS tool usage and optimizations. However, hand-coded RTL may still be better for highly specialized or resource-constrained designs.

Q3: Is HLS suitable for all FPGA projects?

HLS is ideal for projects with complex algorithms and faster iteration needs. Simple or highly optimized designs may still benefit from traditional RTL coding.

Sign in to leave a comment.